### Advantest Corporation IR Technical Briefing Characteristics and Needs of HPC/AI Device Test

November 28<sup>th</sup>, 2024

Akio Osawa, Executive Officer, Senior Vice President, Sales Group and Division Manager, System Solution Division Takashi lino, Functional Manager, Center of Expertise (COE), 93000 Product Unit

#### **Cautionary Statement with Respect to Forward-Looking Statements**

- This presentation contains "forward-looking statements" that are based on Advantest's current expectations, estimates and projections. These statements include, among other things, the discussion of Advantest's business strategy, outlook and expectations as to market and business developments, production and capacity plans. Generally, these forward-looking statements can be identified by the use of forward-looking terminology such as "anticipate," "believe," "estimate," "expect," "intend," "project," "should" and similar expressions. Forward-looking statements are subject to known and unknown risks, uncertainties and other factors that may cause Advantest's actual results, levels of activity, performance or achievements to be materially different from those expressed or implied by such forward-looking statements.

#### **Use of These Materials**

- The information contained in this presentation is protected under intellectual property laws, such as copyright law, patent law, trademark law and design law, and other laws and statutes of each country and various treaties. Any use (modification, copying, diversion, etc.) of this information that goes beyond that which is clearly authorized by law and statutes, and is not approved in writing by our company in advance, is forbidden.

### ✓ Business Environment of SoC testers

✓ Characteristics and Needs of HPC/AI Device Test

# **Business Environment of SoC testers**

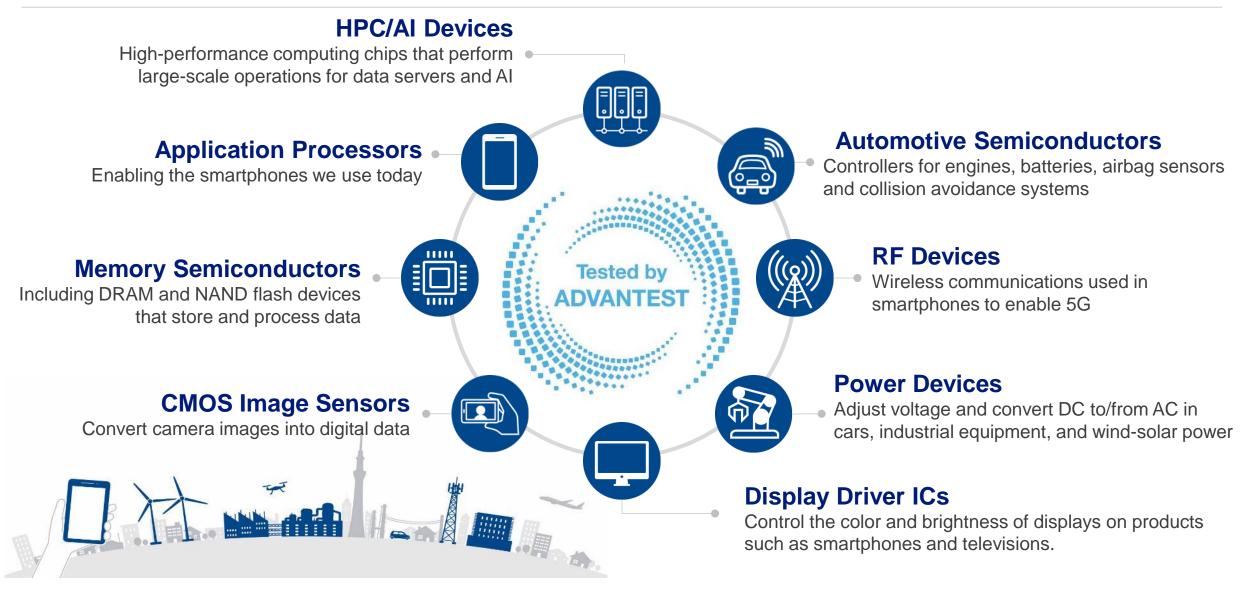

### **The Devices We Test**

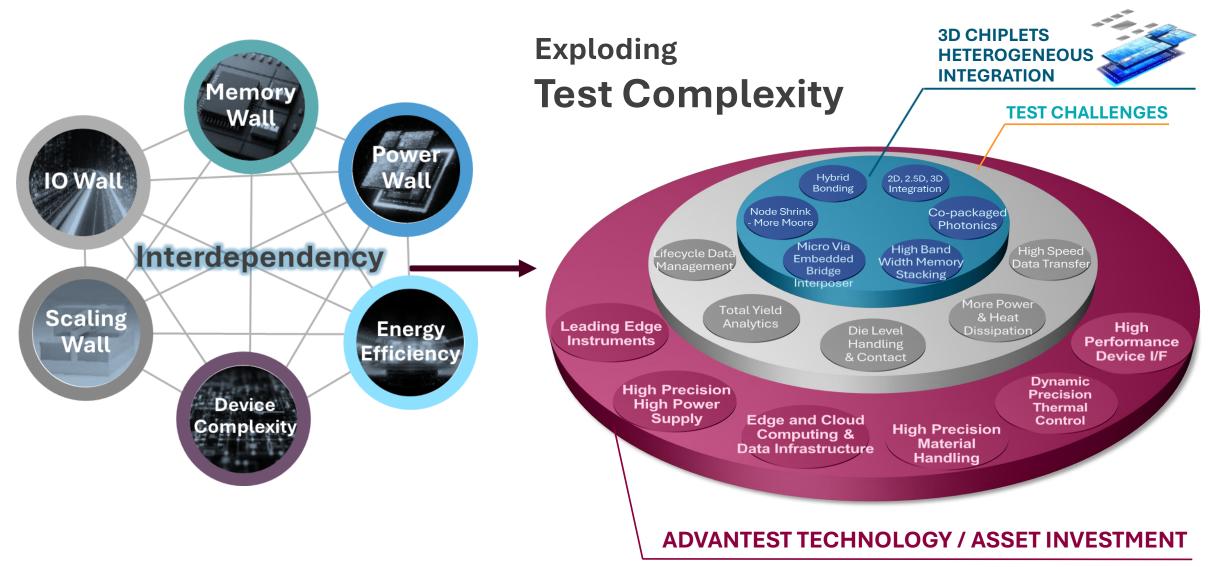

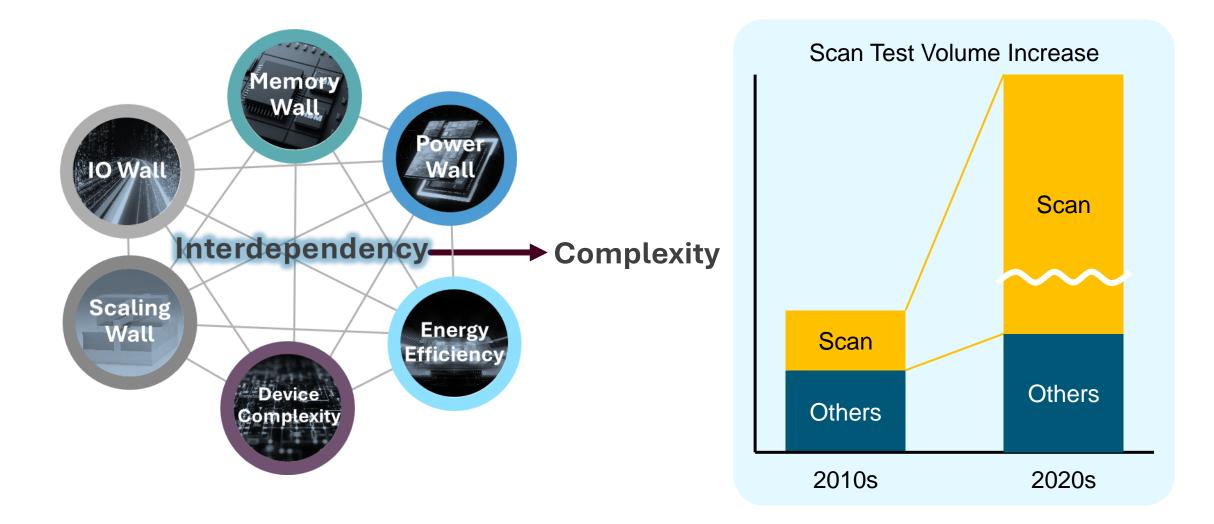

### Acceleration of the "Era of Complexity"

### Acceleration of the "Era of Complexity"

Challenges in semiconductor industry are becoming increasingly complex and mutually interdependent

#### Process (line width) /

#### **Fabrication Technology Miniaturization**

- Shift to GAA. CFET

- Material innovation

- Lithography innovation

- Chiplet, 3D/3.5D

- New failure mechansim

Scaling

Wall

#### Increasing Power Consumption

- Multi-core, accompanied with Thermal Wall

- Efficient power delivery

- Thermal Management

#### **Increasing Memory Complexity**

- In or Near memory computing

- In package high-bandwidth memory +low latency

#### Communication With Faster, More Advanced Protocols

- New Network Architecture

- Chiplet connection

- Co-packaged Optics + copper

Energy

Efficiency

#### **Device Structure Complexity**

- System scaling up

- SW, FW, HW Architectures

- Design for 3D, Advanced Packaging

- Test data explosion

- Complex Supply Chain

#### **Power Consumption Reduction**

- Data localization. Cache & memory hierarchy

- Optics die to die link

- 3D integration

- Integrated IVR, PMIC

All Rights Reserved - ADVANTEST CORPORATION

# Characteristics and Needs of HPC/AI Device Test

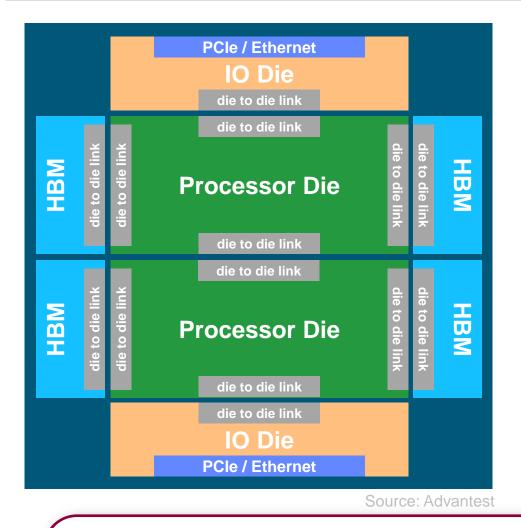

# **Characteristics and Technical Trends of HPC/AI Device**

#### Characteristics

- Chiplet design

- Multiple processor dies

- Multiple IO dies

- Multiple HBM

- Trends

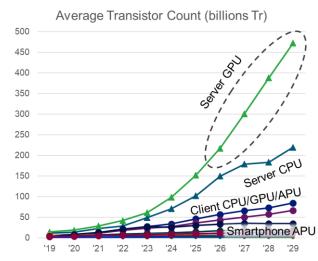

Source: Processor Market Monitor, Q3 2024, Yole Intelligence

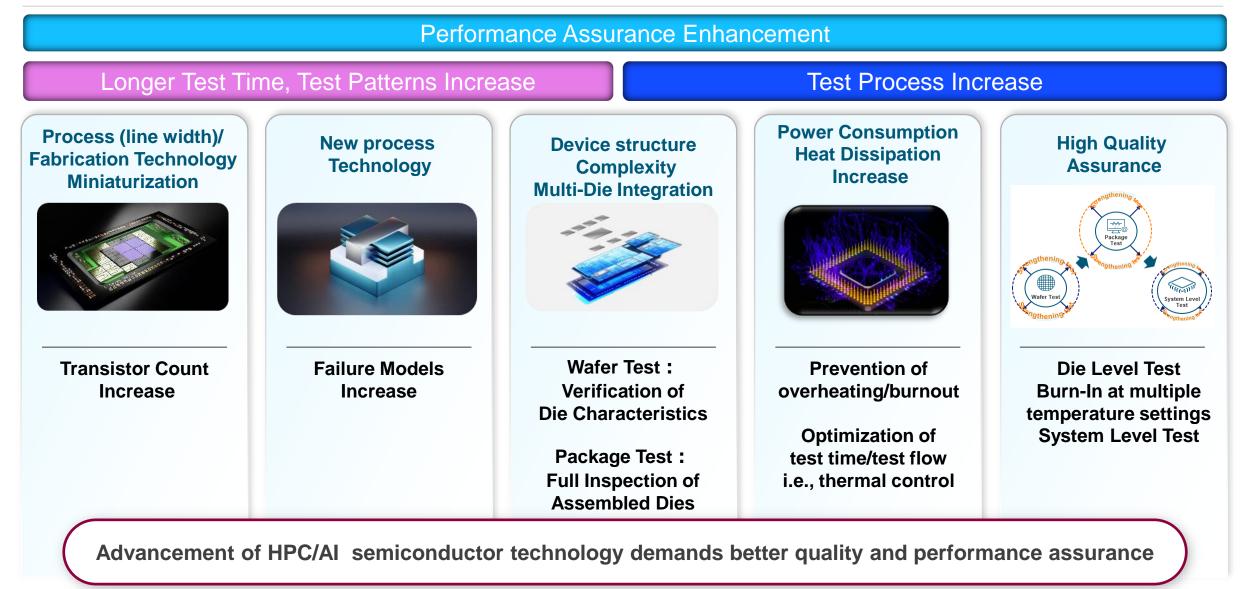

- Miniaturization, new process technology, 3D Assembly, Increase in package size

- Chiplet and multi-die integration to be the industry standard

- Further increase in the bandwidth of IO dies (PCIe5/6, multi-level transmission)

- HBM with higher speed, increased complexity, and further increase in stacking

Multiple large dies are integrated and must be efficiently tested in a short period of time

**ADVANTEST**

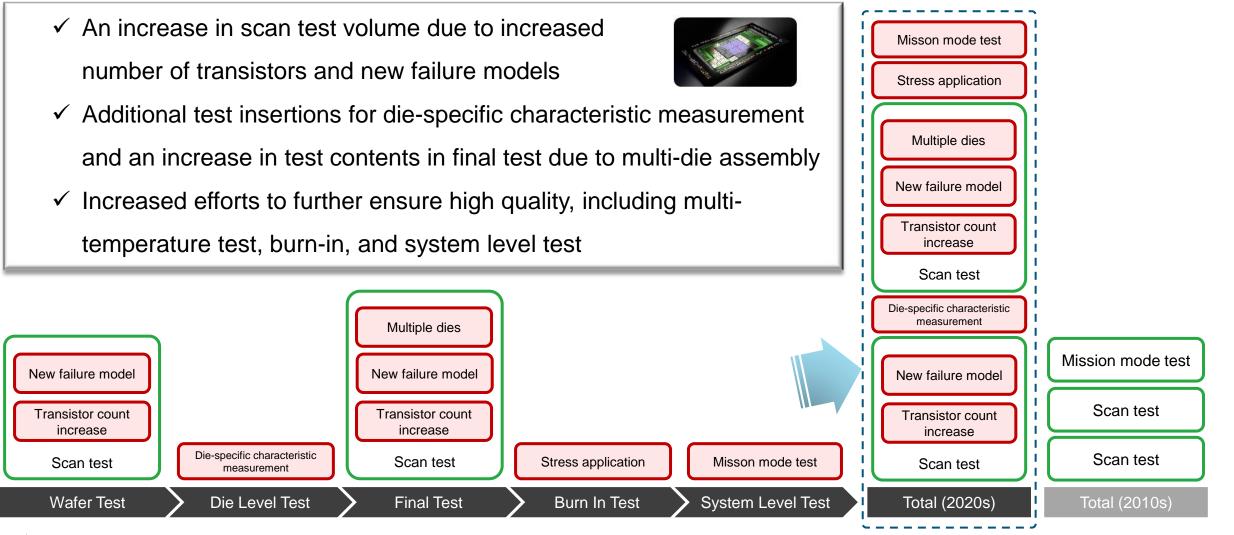

### **Structural Factors Contributing to HPC/AI Test Volume Increase**

10 **ADVANTEST**,

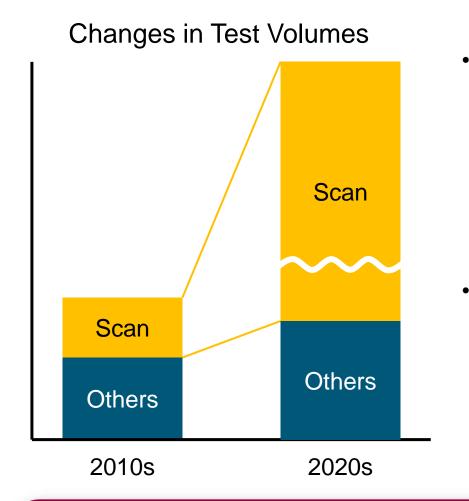

# **Expanding Test Content and Increasing Scan Volume**

• 2010s

- DC test

- BIST<sup>[1]</sup> test including SRAM and high-speed interface etc.

- Functional test

- Scan test

[1] Built In Self Test (BIST) : Test-dedicated circuits designed within the device for testability

#### • 2020s

- Basic test items are largely unchanged

- DC test slightly increased with increasing pin counts

- BIST test growth due to enhanced device functionality

Exponential increase in the number of transistors caused an explosive growth in scan test volume

### **Test and Characteristics of HPC/AI Devices**

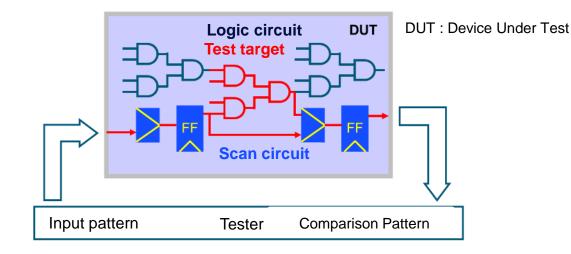

#### Device output Input pattern 1101010110 0001010001 0101100111 0100011001 0100101001 1010111111 1101100011 1001001010 0110111000 Input Output 0010100000 Comparison Pass/fail Comparison pattern 1101011001 0101100111 0100101001 1101100011 0010100000

### **HPC/AI** Devices Logic Testing

### Scan test

- Typical item of DFT (Design for Testability)

- Main test item for SoC devices from the 2000s to the present

- Scan circuits are inserted in the device to arbitrarily set conditions of the sites to be measured

- · Generate test patterns based on assumed failure models and locations

- High efficiency /high test coverage (95 to 99.5%)

Increasing transistor count causing lengthening of "test patterns" = Lengthening of test time

12 **ADVANTEST**

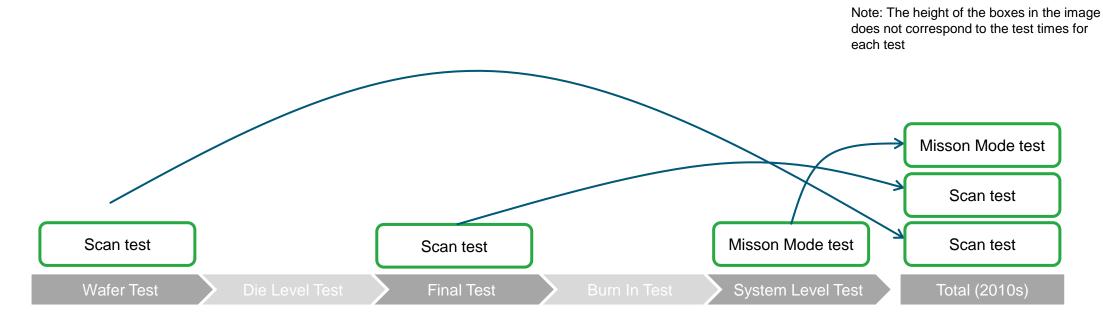

### Test in the 2010s: Screening of Defective Devices

- ✓ Wafer Test : test each die individually, Final test : test each packaged die individually

- ✓ Test Volume : Wafer Test = Final Test (Package Test)

- ✓ Test items optimized for front-end and back-end processes, respectively

- ✓ System level test is added depending on the application

13 **ADVANTEST**

### Test in the 2020s: More Complex, Longer Test Time

Note1: The height of the boxes in the image does not correspond to the test times for each test. Note2: Items in the red boxes are factors driving demand growth in the 2020s.

### Test Demand Driven by Accelerating "Complexity"

15 **ADVANTEST**,

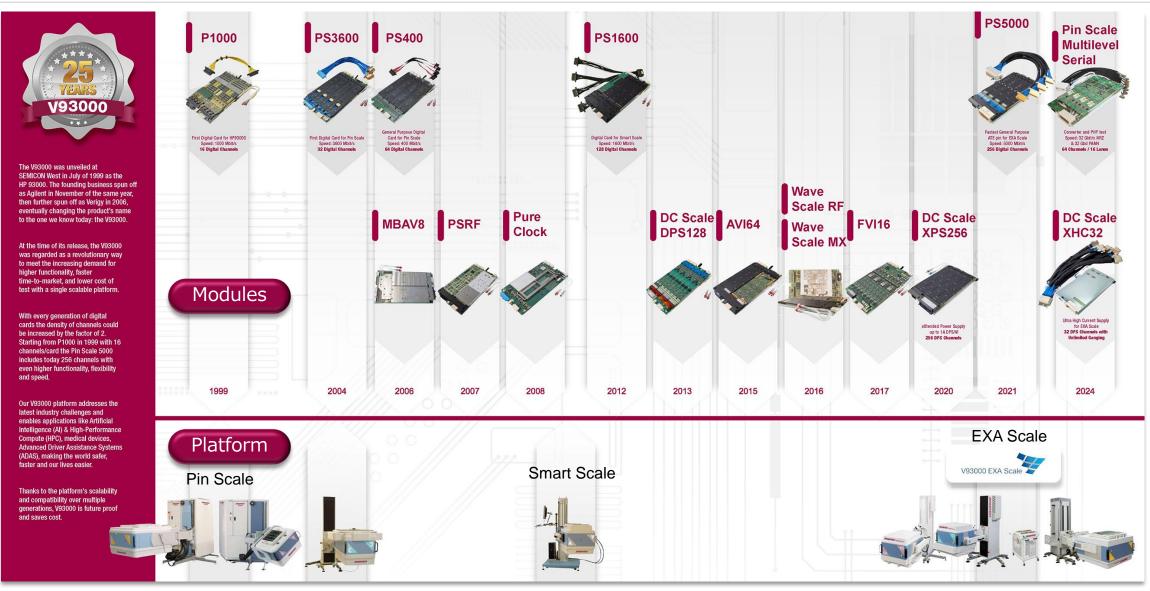

### **V93000 - The Scalable SoC Test Platform**

Facing the future together