## Advantest IR Technical Briefing Test Needs and Solutions in the Memory Semiconductor Market

November 29<sup>th</sup>, 2023 Masayuki Suzuki, Executive Vice President Memory Test Business Unit, ATE Business Group

Jin Yokoyama, Department Manager Memory Test Business Unit, ATE Business Group

#### **Cautionary Statement with Respect to Forward-Looking Statements**

This presentation and any information provided orally by Advantest representatives contains "forward-looking statements" that are based on Advantest's current expectations, estimates and projections. These statements include, among other things, the discussion of Advantest's business strategy, outlook and expectations as to market and business developments, production and capacity plans. Generally, these forward-looking statements can be identified by the use of forward-looking terminology such as "anticipate," "believe," "estimate," "expect," "intend," "project," "should" and similar expressions. Forward-looking statements are subject to known and unknown risks, uncertainties and other factors that may cause Advantest's actual results, levels of activity, performance or achievements to be materially different from those expressed or implied by such forward-looking statements.

#### **Use of These Materials**

- The information contained in this presentation is protected under intellectual property laws, such as copyright law, patent law, trademark law and design law, and other laws and statutes of each country and various treaties. Any use (modification, copying, diversion, etc.) of this information that goes beyond that which is clearly authorized by law and statutes, and is not approved in writing by our company in advance, is forbidden.

## ✓ Memory Tester Business Environment

✓ Test Needs and Solutions in the Memory Semiconductor Market

# **Memory Tester Business Environment**

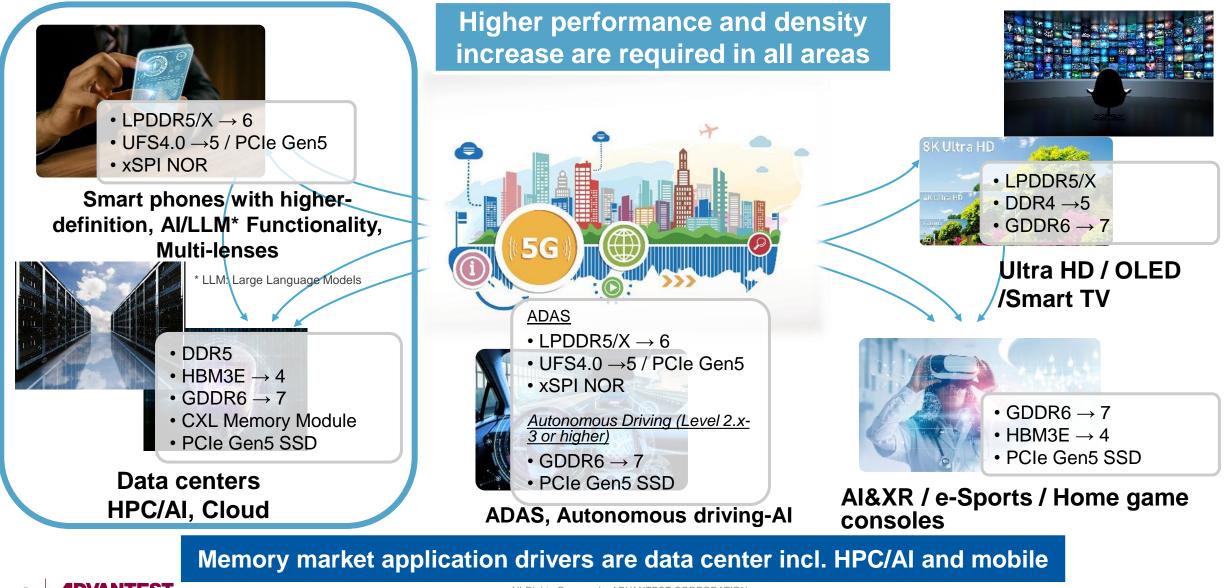

## **Key Applications Driving the Next-Generation Memory Market**

5 **ADVANTEST**,

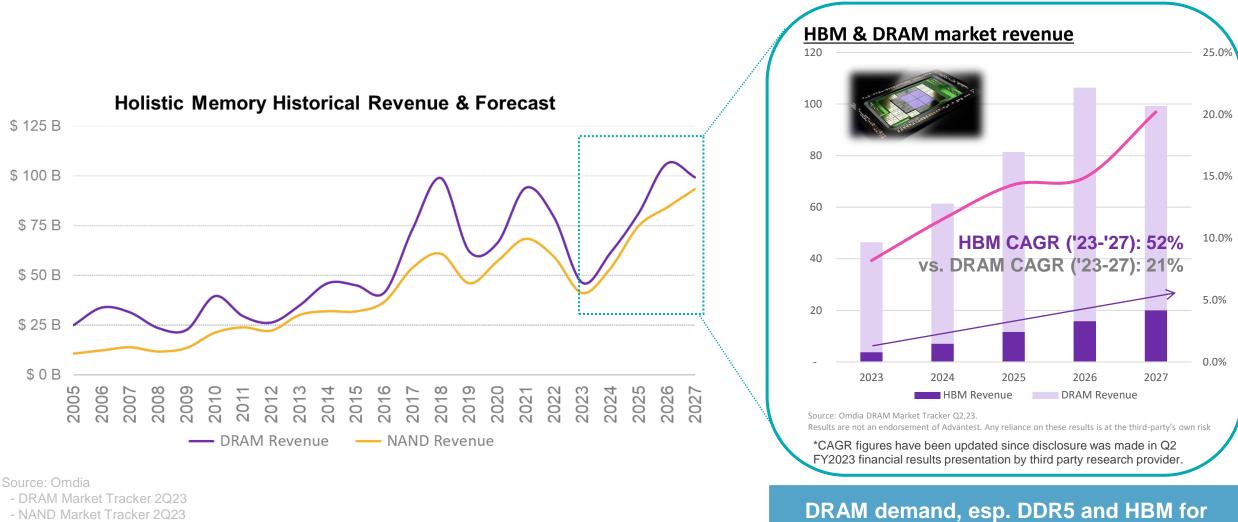

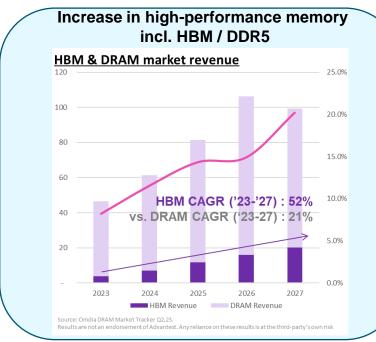

## **High-performance DRAM for HPC/AI Drives the Market**

- NAND Market Tracker 2Q23

- Mobile & Embedded Memory Market Tracker 2Q23

Results are not an endorsement of Advantest. Any reliance on these results is at the third-party's own risk.

HPC/AI servers, is driving the market

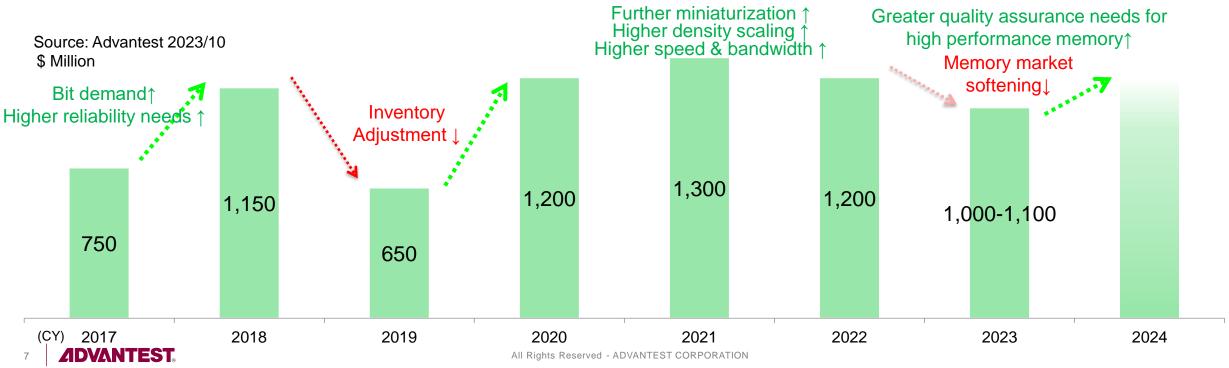

## **Memory Tester Market Trends**

- Density increase, higher interface speeds, and higher reliability assurance are key determinants of an increase in tester demand

- In comparison with the previous down cycle (2019 vs 2023), the decline caused by the memory market deterioration is somewhat offset by an increase in tester demand for high-performance memory such as HBM and DDR5

- In 2024, the market is expected to expand year-on-year due to a recovery in market conditions and an increasing demand trend for high-performance memory

#### Memory Tester Market Transforming into a Less-Cyclical Growth Market

## Core competence to maintain the world's No.1 memory ATE<sup>\*</sup> market share

### Strong technology capabilities and leadership in the memory test industry

- Memory ATE market share in 2022 : 53% (Advantest estimate)

- First to market optimal test solutions in the high-end market Consistently establishing a de facto standard position in the industry

#### Industry's No.1 product portfolio and total solution capabilities

- Extensive product portfolio for all test processes Competitive advantage through comprehensive solutions including peripherals

- Enhancing customer's volume production efficiency through high product quality that delivers the industry's highest MTBF\*\*

- The industry's largest and robust customer base

- Globally positioned expert engineers with the advanced memory testing knowledge and experience accumulated over the years

\*ATE: Automated Test Equipment \*\*: Mean Time Between Failure

Source: Advantest

## Industry's sole supplier covering all memory test processes

## Full solution line up covering memory test processes

## Integrated solutions for memory device technology evolution & supply growth

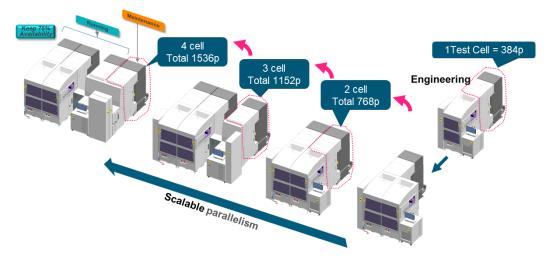

Memory test cell "inteXcell" offers extensive test coverage with integration of high throughput handling technology

- Industry-leading test solutions that integrate the memory test, device interface, and auto handler technologies we have accumulated over the years

- InteXcell addresses memory device package testing challenges such as higher density, power savings, and higher interface speed

- Single platform that covers design evaluation to mass production

inteXcell Series 4Cell Configuration

# Combines scalability of system configuration with minimized footprint

- Flexibly expand parallelism from 364 to 1,536 DUTs\*

\*DUT: device under test

- Footprint reduced to aprx.1/3 of that of conventional products

- Contributing further to production efficiency by controlling each small test cells individually and addressing automation at customers' volume production facilities

## Memory Semiconductor Testing Needs and Solutions

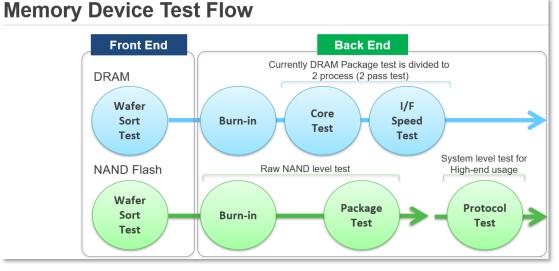

## **Memory Semiconductor Test Flow and Features**

#### Memory Test Features

- Test flow set up from wafer to package according to test menus and temperature environment

- High parallelism is crucial to optimize throughput according to the technological evolution of memory

- Requirements becoming more rigorous as generation changes have led to higher test speeds and higher reliability assurance needs

#### Key drivers of memory test/tester demand

- Bit growth (# of chip shipped x memory density) is critical to test demand Transition to advanced processes such as miniaturization of DRAM and increasing 3D-NAND layer count leads to bit growth and longer test time, causing tester demand to grow for each test flow

- Rise in memory data transmission speed creates new demand for high-speed testers

DRAM interface speed test process requires testers with new test coverage

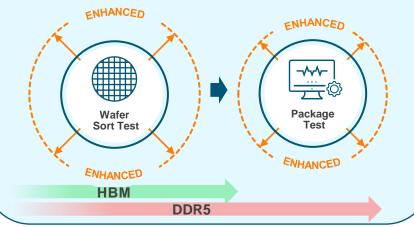

- Increase in production volume of high-performance memory semiconductors for AI/HPC with high reliability requirements For HBM, tester demand increases due to more elaborate testing and additional test insertions post stacking driven by higher reliability requirements alongside adoption of advanced packaging

#### Test needs and technology challenges for next generation memory

####

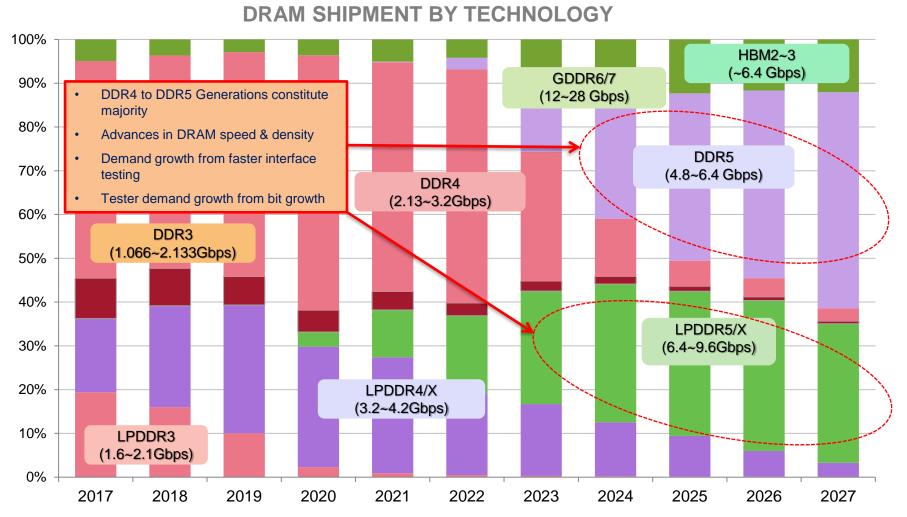

## **DRAM Interface Trend Forecast**

Source: Omdia DRAM Market Tracker Q2,23.

Results are not an endorsement of Advantest. Any reliance on these results is at the third-party's own risk

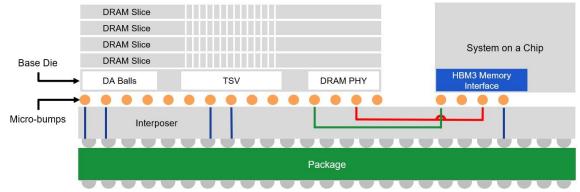

## High-bandwidth memory HBM supporting social implementation of gen. Al

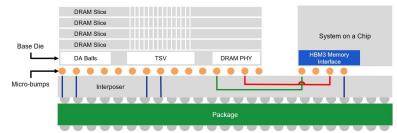

#### What is HBM (High Bandwidth Memory)?

- A type of 3D stacked memory technology. Higher bandwidth and density scalability than conventional 2D memory

- Challenges exist for advanced packaging such as 2.5D/3D with increased manufacturing costs and thermal control. Used primarily in high-performance HPC/AI computing

- Latest HBM3 offers 12 times higher density and 13 times higher bandwidth than GDDR6

HBM3 Memory Interface (Source: Rambus Inc.)

High market growth rate is expected as GPUs with high parallel processing with thousands of cores or more and HBM with its optimal configurations are essential for AI technology, which requires enormous computing power

####

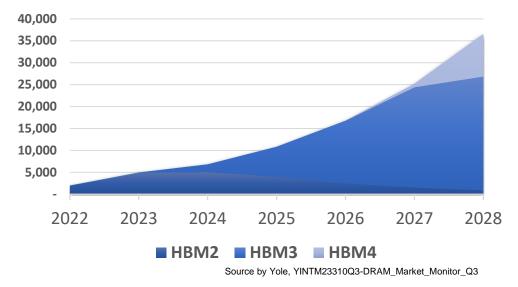

## **HBM Technology Trends and Outlook**

Rapid expansion from HBM3 to HBM4 generation over the next 5 years, led by AI modules for data centers

HBM Shipments (m Gb)

- HBM CAGR of 49% from 2023-2028 (bit base) ۰

- Rapid share expansion of HBM3 (incl. enhanced versions) after 2024

- New process development, addressing issues such as ٠ thermal and cost, is expected for the next generation HBM

Interface speed, bandwidth, stack count, and density expected to double with each generation

#### HBM2E HBM3 HBM4 Memory 460GB/s >820GB/s >1.5TB/s bandwidth Density 8/16Gb 16/24Gb 24/32Gb per die Stack 4, 8 8, 12 8, 12, 16 count **IO Speed** 3.2 Gbps >6.4Gbps TBD

**Performance Comparison by HBM Generation**

Includes Advantest Marketing Estimation

- Bandwidth performance growing multiple-fold from HBM2E, HBM3, its enhanced versions, and to HBM4 generation

- Memory density increases as the HBM stack count changes to 4-8-12-16 stacks, along with the miniaturization of the individual die

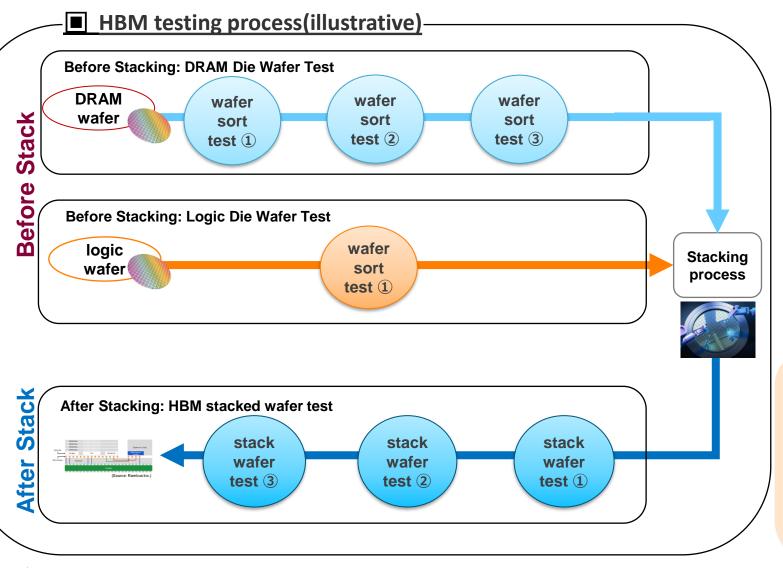

## **Current HBM testing process and issues**

HBM3 Memory Interface (Source: Rambus Inc.)

#### Test Challanges

- Each new generation leads to increased density & stacks (8->12->16 stacks)

- →Longer test time

٠

.

- Each new generation leads to higher interface speed

- →Higher test speed/increased load on peripheral circuits

- Increase in power supply & current capacity

- → Tester scalability, impact on parallelism

- Yield impact before and after HBM stacked wafer dicing (e.g., die level test)

## Business opportunities for memory testers arising from gen. Al

\*CAGR figures have been updated since disclosure was made in Q2 FY2023 financial results presentation by third party research provider.

Rising quality assurance requirements due to higher functionality and complexity growth

# Increase in advanced packages incl. 2.5D/3D

## **Memory Tester Business Environment and Growing Test Demand**

## Continued increase in memory performance & density in all areas

- Data centers incl. HPC/AI and mobile to drive the memory market

- Rapid adoption of gen. AI and advanced LLMs increases demand for high-performance AI modules (GPU+HBM)

- In particular, high-performance memory such as HBM and DDR5 to drive the market

Memory semiconductor production volume to increase due to broadening of applications

Tester demand to grow for HBM in response to expanding production plans by customers

Semi Technology Evolution "Technology Buy"

Bit growth accelerated by transition to advanced processes, causing test time to increase

Increasing memory speeds create demand for faster interface test

#### Higher quality & reliability needs "Quality Buy"

Higher quality assurance needs for high-end memory leads to more elaborate testing, causing test time to increase

Supporting the technological evolution & growing demand of memory devices with "Tested by Advantest," contributing to the realization of "safety, security, & comfort" of society