-

Products

Advantest Unveils SiConic Test Engineering: Unified, Scalable Bench Environment for Debug and Validation

-

Investors

Presentation Material "Fiscal 2024 Consolidated Financial Results" updated

-

Investors

FY2024 Consolidated Financial Results

-

Investors

Share Repurchase

-

Investors

Notice regarding Appointments of Directors and Executive Officers

-

Topics

Emerson and Advantest Join Forces to Deliver AI-Driven Test Ecosystem Enabling Real-Time Edge Analysis and Decision Making

-

Events

Advantest to Showcase Latest IC Test Solutions at SEMICON China 2025, March 26-28 in Shanghai

-

Investors

FY2024 Consolidated Financial Results is planned to be announced on Apr. 25 (15:30 JST)

-

Sustainability

Advantest Receives "White 500" Certification from METI for Fifth Consecutive Year

-

Events

Advantest to Showcase IC Test Solutions at IESA Vision Summit 2025, March 5-7 in Gujarat, India

-

Topics

Advantest Forms Strategic Partnerships with Micronics Japan

-

Topics

Data Management Frontiers: Navigating the Semiconductor Landscape with Joe Addiego of Brave Capital

-

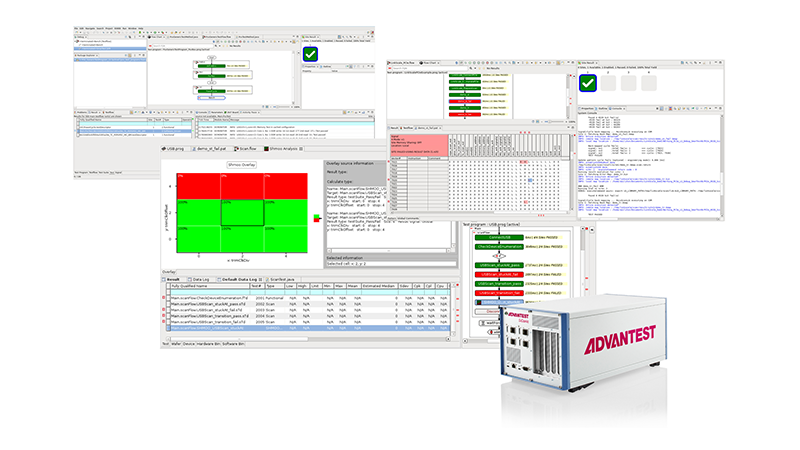

Products

Advantest Introduces SiConic: Groundbreaking Solution for Automated Silicon Validation

-

Events

Advantest to Showcase Latest Test Solutions at SEMICON Korea 2025, Feb. 19-21, in Seoul

-

Products

Advantest Unveils T5801 Ultra-High-Speed Memory Test System to Power Next-Generation DRAM Devices

-

Topics

Advantest Supports Victims of Wildfires in Southern California

-

Events

Advantest Opens Registration for International VOICE 2025 Developer Conference, May 12-14

-

Topics

TechInsights Semiconductor Industry Outlook 2025 and Beyond: Advantest Talks Semi Podcast

-

Investors

Presentation Material "3rd Quarter Fiscal 2024 Consolidated Financial Results" updated

-

Investors

FY2024 Third Quarter (Semi-Annual) Consolidated Financial Results

-

Investors

Revisions of Year-End Dividends Forecast

-

Investors

Status of Share Repurchase and its Completion

-

Investors

Revision of Earnings Forecast for the Fiscal Year Ending March 31, 2025

-

Sustainability

Advantest Receives Platinum Kurumin Certification

-

Topics

Advantest Forms Strategic Partnerships with FormFactor and Technoprobe

-

Investors

Status of Share Repurchase (Under the provisions of its Articles of Incorporation pursuant to Article 459, paragraph 1 of the Companies Act)

-

Topics

Group CEO Lefever 2025 New Year’s Address (Summary)

-

Sustainability

Advantest Selected for the Third Consecutive Year for DJSI Asia Pacific

-

Topics

Are Silicon Photonics the Only Way Forward in Semiconductors?: Advantest Talks Semi Podcast

-

Investors

FY2024 3rd Quarter Consolidated Financial Results is planned to be announced on Jan. 29 (15:30 JST)

-

Events

Advantest to Showcase Latest Test Solutions at SEMICON Japan 2024, Dec. 11-13, in Tokyo

-

Products

Advantest Launches KGD Test Cell for Power Semiconductors

-

Products

Advantest Launches ACS Gemini™ – New Developer Platform for Accelerating ACS RTDI™ Application Development

-

Investors

Status of Share Repurchase

-

Investors

IR Technical Briefing Presentation Material (HPC/AI Device Test)

-

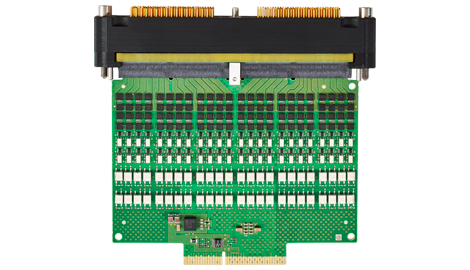

Products

Advantest Announces Advanced Power Multiplexer for V93000 EXA Scale Test Platform

-

Products

Advantest Rolls Out Wave Scale RF20ex: High-Frequency, High-Bandwidth RF IC Test Card for V93000 EXA Scale Platform

-

Events

Advantest to Showcase Latest Test Solutions at SEMICON Europa 2024, Nov. 12-15, in Munich, Germany

-

Investors

Presentation Material "2nd Quarter Fiscal 2024 Consolidated Financial Results" updated

-

Investors

FY2024 Second Quarter (Semi-Annual) Consolidated Financial Results

-

Investors

Share Repurchase

-

Investors

Interim Dividends for the Fiscal Year Ending March 31, 2025

-

Events

Advantest to Showcase Latest Semiconductor Test Solutions at the 2024 International Test Conference in San Diego, California

-

Topics

Advantest Ranked 3rd in Forbes JAPAN's "100 Great Companies" Stakeholder Capitalism Ranking

-

Topics

Advantest Awarded 2024 Porter Prize

-

Sustainability

New! Four Seasons of Advantest's Biotope Enjoy this video showcasing the beauty of the biotope around the year.

-

Topics

Beyond Black Boxes: Meet AI that Justifies Its Choices: Advantest Talks Semi Podcast

-

Investors

Integrated Annual Report 2024 now Available

-

Events

Advantest Announces Call for Papers for VOICE 2025 Developer Conference in Austin, Texas

-

Topics

Advantest Wins 2024 Supplier of the Year Award from Qualcomm

-

Topics

How to Advance Chip Design with Digital Twins and EDA: Advantest Talks Semi Podcast

-

Investors

FY2024 2nd Quarter Consolidated Financial Results is planned to be announced on Oct. 30 (15:00 JST)

-

Events

Advantest to Showcase IC Test Solutions at Inaugural SEMICON India, Sept. 11-13, 2024 in Greater Noida

-

Events

Advantest to Highlight Latest Semiconductor Test Solutions at SEMICON Taiwan 2024, Sept. 4-6 in Taipei

-

Topics

Advantest Tech Podcast – Why you should tune in!: Advantest Talks Semi Podcast

-

Topics

Advantest Celebrates 25th Anniversary of Industry-Leading V93000 SoC Test Platform

-

Events

Advantest will Showcase Latest Memory Test Solutions at Future of Memory and Storage 2024

-

Investors

Presentation Material "1st Quarter Fiscal 2024 Consolidated Financial Results" updated

-

Investors

FY2024 First Quarter Consolidated Financial Results

-

Investors

Revisions of Interim Dividends Forecast

-

Investors

Revision of Earnings Forecast for the Fiscal Year Ending March 31, 2025

-

Investors

Completion of Disposal of Treasury Stocks based on Post-issued Restricted Stock Unit Remuneration Plan and Performance Share Unit Plan

-

Investors

Notice regarding Completion of Disposal of Treasury Stocks as Restricted Stock

-

Topics

Advantest Europe GmbH becomes New Club Partner of VfB Stuttgart

-

Sustainability

New! Biotope Virtual Tour Experience a stunning 360-degree virtual tour of Advantest's biotope.

-

Products

Advantest Achieves ASPICE Level 2 Certification for V93000 SmarTest 8 Software

-

Events

Advantest to Showcase Latest Test Technology at SEMICON West 2024, July 9-11, in San Francisco

-

Topics

Advantest Celebrates 70 Years of Enabling Leading-Edge Technologies ~Facing the Future Together~

-

Investors

Notice Regarding Resolution Adopted at the 82nd Ordinary General Meeting of Shareholders

-

Investors

Notice regarding Disposal of Treasury Stock as Restricted Stock

-

Investors

Notice regarding Disposal of Treasury Stock based on Post-issued Restricted Stock Unit Remuneration Plan and Performance Share Unit Plan

-

Events

Advantest’s VOICE 2024 Draws Record Attendance in San Diego

-

Investors

Advantest’s View & Policy on the Reduction of Investment Units

-

Investors

Presentation Material "Third Mid-Term Managemant Plan" updated

-

Investors

Advantest Announces Formulation of the Third Mid-term Management Plan (FY2024-FY2026)

-

Products

Advantest Launches New nanoSCOUTER™ Particle Measuring Equipment

-

Investors

FY2024 1st Quarter Consolidated Financial Results is planned to be announced on Jul. 31 (15:00 JST)

-

Investors

Announcement of Mid-/Long-Term Management Policy is planned to be announced on June 25 (15:00 JST)

-

Investors

Convocation Notice of the 82nd Ordinary General Meeting of Shareholders (Delivery date of Convocation Notice (Notice of Access) and Dividend Documents is June 6th.)

-

Investors

Distribution of the Year-End Dividends from Surplus

-

Investors

Notice regarding Disposal of Treasury Stock based on the Post-issued Restricted Stock Unit Plan

-

Events

Advantest to Exhibit Latest Test Solutions at SEMICON Southeast Asia, May 28-30

-

Topics

Advantest Ranks THE BEST Assembly Test Equipment Supplier and the #1 Large Supplier of Chip Making Equipment in 2024 Customer Satisfaction Survey

-

Products

Advantest Unveils New Ultra-High-Current Power Supply for V93000 EXA Scale SoC Test System

-

Investors

FY2023 Consolidated Financial Results

-

Investors

Revisions of Year-End Dividends Forecast

-

Investors

Presentation Material "Fiscal 2023 Consolidated Financial Results" updated

-

Topics

Advantest Supports Victims of Taiwan Earthquake

-

Topics

Advantest & Toray Engineering Establish Technical Partnership

-

Topics

Advantest Reports no Direct Impact from the Eastern Taiwan Earthquake

-

Sustainability

Advantest Receives "White 500" Certification from METI for Fourth Consecutive Year

-

Investors

FY2023 Consolidated Financial Results is planned to be announced on Apr. 26 (15:00 JST)

-

Events

Advantest to Exhibit Latest Test Solutions at SEMICON China, March 20-22 in Shanghai

-

Topics

Notice of Changes of Representative Directors

-

Sustainability

Biotope Quarterly has been updated. Leafless trees in winter are introduced.

-

Sustainability

Advantest Selected for S&P Sustainability Yearbook 2024

-

Events

Advantest Opens Registration for International VOICE 2024 Developer Conference, June 3-5

-

Investors

Presentation Material "3rd Quarter Fiscal 2023 Consolidated Financial Results" updated

-

Investors

FY2023 Third Quarter Consolidated Financial Results

-

Topics

Advantest Supports Victims of 2024 Noto Peninsula Earthquake