東北大学CIESとの共同研究、STT-MRAMの開発効率向上と量産化に寄与

株式会社アドバンテスト(本社:東京都千代田区 代表取締役 兼 執行役員社長:吉田 芳明)は、国立大学法人東北大学(総長:大野 英男/以下、東北大学)国際集積エレクトロニクス研究開発センター(以下、CIES)の遠藤 哲郎センター長(兼 同大学大学院工学研究科教授)のグループと共同で、当社メモリ・テスト・システムを用いて、次世代メモリとして期待されている「スピン注入型磁気ランダム・アクセス・メモリ(STT-MRAM)」の歩留まり率向上と高性能化の実証実験に成功しました。

今回の実証実験の成果は、STT-MRAM向けテスト・システム実用化への大きな一歩であり、STT-MRAMの開発効率向上と量産への貢献につながるものです。

半導体メモリは、技術の進歩とともに大容量化、高速化が進んできました。しかし現在、高速メモリの主流であるDRAMなどの揮発性メモリは、待機電力の増加という問題に直面しています。NANDフラッシュなどの不揮発性メモリは、電力無しで情報を保持できるものの、高速動作や書き換え耐性等の面で課題を残しています。

現在、これらの問題を解決するために、磁石の性質を用いた不揮発性メモリであるMRAMの研究・開発が盛んに行われています。中でも、電子が持つ電荷の性質と磁石の性質の両方を利用したSTT-MRAMは、他の不揮発性メモリでは実現が難しいとされる高速動作、低電圧動作、高書き換え耐性の特性を全て有し注目を集めています。

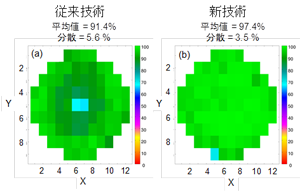

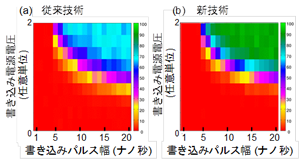

STT-MRAMの性能評価に際して、当社はCIESと共同で、メモリ・テスト・システム「T5385ES」をベースに、電気的特性と磁気的特性をあわせ持つSTT-MRAM特有の不良モードを検知可能な、新たな高速テスト・システムを開発しました。そのシステムを用いて、従来の加工技術と新しい加工技術(反応性イオンエッチング:RIE)で加工された、2種類のSTT-MRAMの300 mmウエハ全面を評価した結果、新加工技術によって歩留まり率が91%から97%に改善することを確認しました(図1)。また、高速動作特性の向上も明らかにしました(図2)。

今回の成果は、5月13日~16日に京都で開催された国際学会「米国電気電子学会 国際メモリワークショップ(IEEE International Memory Workshop)」で発表済みです。

また、詳細につきましては、東北大学のプレスリリースをご参照ください。

-

※本ニュースリリースに掲載されている情報は、発表日現在の情報であり時間の経過またはさまざまな事象により予告無く変更される可能性がありますので、あらかじめご了承ください。