東北大学CIESとの共同研究、STT-MRAMの不良解析と実用化に大きく前進

株式会社アドバンテスト(本社:東京都千代田区 代表取締役 兼 執行役員社長:吉田 芳明)(以下当社)は、指定国立大学法人東北大学国際集積エレクトロニクス研究開発センター(以下東北大学CIES)の遠藤 哲郎センター長(兼 同大学大学院工学研究科教授)のグループと共同で、次世代メモリとして期待される「スピン注入型磁気ランダム・アクセス・メモリ(STT-MRAM)」のメモリ・アレイ内のスイッチング電流を測定するモジュールを開発し、当社メモリ・テスト・システムを用いてマイクロアンペア単位かつナノ秒単位で測定する実証実験に成功しました。

これにより、STT-MRAMのメモリセル内に流れる微小な電流の変化を観察可能となり、STT-MRAMの不良解析、ひいては同技術を用いたメモリ・テスト・システムの実現によりSTT-MRAMの実用化に向けて大きく前進しました。また、当技術は STT-MRAMだけでなく、他の抵抗変化型メモリであるReRAMやPCRAMにおいても有効な技術です。

STT-MRAMは、磁気トンネル接合と呼ばれる磁石を用いた素子を、碁盤目状に並べて(メモリ・アレイ)作成されます。磁気トンネル接合は、磁石の磁化方向に依存して抵抗が変化する性質を示すことから、その磁化の方向を記憶の媒体として、情報を記憶することができます。磁石の性質は電源を切っても失われない、待機電力が不要な不揮発性メモリであることに加え、他の不揮発性メモリでは実現が難しいと言われている高速動作、低電圧動作、高書き換え耐性の特性を全て備えていることから、世界中の研究機関や企業で研究開発が行われています。

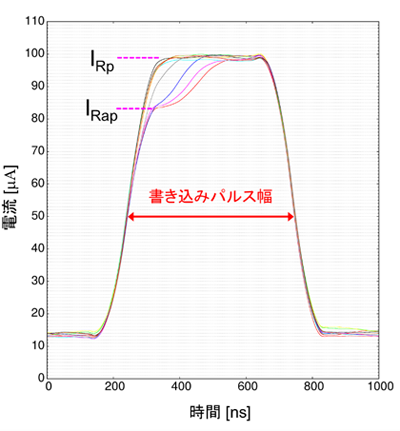

STT-MRAMの開発および量産には、メモリ・テスト・システムによる高効率、高精度な性能評価が不可欠です。しかし、STT-MRAMの記憶素子のスイッチングは、熱エネルギーによる揺らぎの影響を受けた確率的な現象であることに加えて、そのスイッチングに必要となる電流が100マイクロアンペア以下と非常に小さく、しかもナノ秒単位の短時間にしか流れません。そのため、計測器を用いて磁気トンネル接合1つのスイッチングの測定はできても、メモリ・アレイ内のメモリセル上でスイッチングの測定を行うことは困難でした。

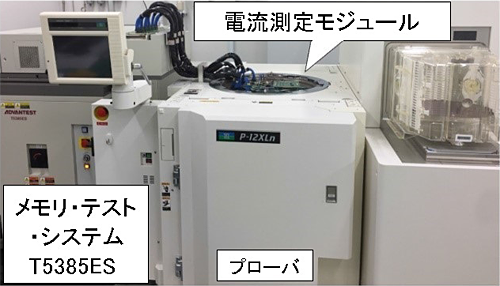

今回、当社は東北大学CIESと共同で電流測定モジュールを開発し(図1)、当社製メモリ・テスト・システムを用いて、STT-MRAMのスイッチング動作時の微小な電流値変化と、スイッチング試行ごとのナノ秒単位の電流遷移時間を測定する実験に成功しました(図2)。実験では、産業界で標準的に使用されている直径300mmのSiウェハ上に試作した、1つのMTJと1つのトランジスタで構成されるメモリセルによるSTT-MRAMテストチップを用いて、ウェハ全面で測定を行いました。今回の成功により、STT-MRAMの高効率かつ高精度な不良解析が可能となりました。この解析技術を用いることで、STT-MRAMの歩留まり率の向上、ひいてはSTT-MRAMの実用化へとつながります。

このマイクロアンペア単位・ナノ秒単位のわずかな差をメモリ・テスト・システムで測定可能にした。

今回の実証実験の成功は、CIESコンソーシアムに於ける共同研究および、「OPERA *(科学技術振興機構 産学共創プラットフォーム共同研究推進プログラム)」の開発体制によるものです。東北大学CIESでは、外部磁界印加機構を搭載したSTT-MRAM評価用の新たなメモリ・テスト・システムの製品化を目指して、引き続き研究開発活動を進めます。

なお、当成果については、2018年10月22日~24日に仙台で開催された国際学会「米国電気電子学会 不揮発性メモリ技術シンポジウム(IEEE Non-volatile Memory Technology Symposium)」で発表しました。

-

*OPERAは、東北大学が幹事機関を務め、東北大学・京都大学・山形大学と先進的企業群の力を結集して、産学共創プラットフォームの形成を目指すJST(科学技術振興機構)のプログラムです。

-

※本ニュースリリースに掲載されている情報は、発表日現在の情報であり、時間の経過、または、さまざまな事象により予告無く変更される可能性がありますので、あらかじめご了承ください。