株式会社アドバンテスト(本社:東京都千代田区 代表取締役 兼 執行役員社長:吉田 芳明)(以下当社)は、指定国立大学法人東北大学国際集積エレクトロニクス研究開発センター(以下東北大学CIES)の遠藤 哲郎センター長(兼 同大学大学院工学研究科教授)のグループと共同で、次世代メモリとして期待される「スピン注入型磁気ランダム・アクセス・メモリ(STT-MRAM)」の高速動作実証実験に成功しました。

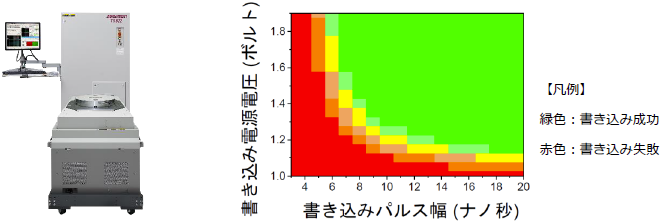

今回の実験では、CIES 産学共同研究プロジェクト「不揮発性ワーキングメモリを目指したSTT-MRAM とその製造技術の研究開発」プログラムで開発された128 Mb密度のSTT-MRAMを、当社製メモリ・テスト・システムを用いて測定しました。実験の結果、従来の半導体集積回路で用いられる電圧と同程度の1.2 Vで書き込む場合には14ナノ秒、1.3 V では一般的なSRAMと同程度の10ナノ秒 で書き込むことができ、STT-MRAMの高速動作を確認しました。実験を通じて、大容量STT-MRAM の高速動作のポテンシャルと、STT-MRAMの量産化に不可欠な高速メモリ特性評価技術の有効性を実証しました。

今回の実証実験の成功は、CIESコンソーシアムに於ける共同研究および「OPERA(科学技術振興機構 産学共創プラットフォーム共同研究推進プログラム)」の開発体制によるものです。東北大学CIESおよび当社は、STT-MRAM評価用の新たなメモリ・テスト・システムの製品化を目指して、引き続き研究開発活動を進めます。

以上の成果は、2018 年12 月5 日(現地時間)、米国サンフランシスコで開催される電子デバイスに関する国際学会「米国電気電子学会国際電子デバイス会議(IEEE International Electron Devices Meeting)」で発表いたします。

右)本実験での128 Mb密度STT-MRAM内サブアレイの高速動作特性評価結果

-

※本ニュースリリースに掲載されている情報は、発表日現在の情報であり、時間の経過またはさまざまな事象により予告無く変更される可能性がありますので、あらかじめご了承ください。